ARM推新數據連接器 準備迎接新處理器架構

點(diǎn)擊:0次 責任編輯:未知 發表(biǎo)時間:2015-10-29 14:07:57

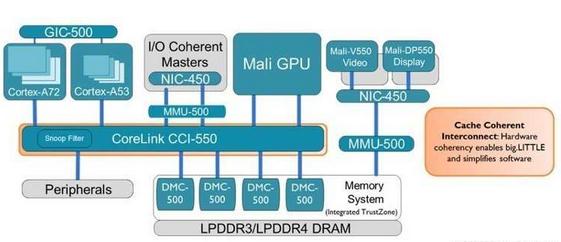

繼先前將CoreLinkCCI-500連結器應用在(zài)Cortex-A72核心(xīn)架構設計,ARM稍早宣布推出全新CoreLinkCCI-550連結器,並(bìng)且加(jiā)入多核(hé)心多叢集配置功能,預期下(xià)一波處理器核心架構可能同樣(yàng)導入多叢(cóng)集(Cluster)運(yùn)作模式,亦即將如同聯發科Helio係列處理器所(suǒ)主推“多檔”運作模式。

ARM推新數據連接器 準備(bèi)迎(yíng)接新處理器架構

根據ARM公布消息,新版CoreLinkCCI-550連結器加入主動偵測(cè)核心運作資料改變時,並且強化資(zī)料存取(qǔ)緩衝頻(pín)寬,將可在處理核心運作資料改變時,強化運算資料同步連結效率(lǜ)。此外,CoreLinkCCI-550連結器(qì)將增加至連結六組處理器核心設(shè)計,架構上也能連結(jié)源自MaliGPU運算資料,藉此實現GPGPU平行運算效果,預期下一代“Mimir”MaliGPU便會支援此項設計。

而因應加(jiā)入最多可連結六組處理器核心,CoreLinkCCI-550連結器(qì)也加入(rù)支(zhī)援最多六組記憶體通(tōng)道(對應(yīng)32-48位(wèi)元定址(zhǐ))、六組ACE主控連接埠等(děng)設計,同時提供最大頻寬可提升60%、資料運算延遲表現降低(dī)20%,此外也能(néng)進一步降低處理器運算耗電量,並且透過平行運算方式(shì)增加整(zhěng)體效能,對於手機、數位電(diàn)視等較耗電能產品均可達成省電目的。

此外,ARM在CoreLinkCCI-550連結器端(duān)也導入DMC-500動態記(jì)憶體控製器,將支援LPDDR3-2133與最高LPDDR4-4267記憶體規格,並且提升27%記憶體頻寬(kuān),同時降低25%處理器資料運算延(yán)遲(chí)率,本身也導入ARMTrustZone技術與DFI4.0PHY介麵工業規範。

目前CoreLinkCCI-550連接器、DMC-500動態記憶(yì)體控製器均預計在2016年下半年間問世,預期ARM也準備公布全新處理器核(hé)心架構設計

本文地址:

http://www.hnpyzjj.com/zixun/xyxw/1503.html轉載時請(qǐng)注明出處。